引言

随着神经网络技术研究的迅速深入,其应用方向不断扩张,在计算机系统结构与专用硬件领域涌现出一批针对各类神经网络进行芯片设计和优化的优秀研究工作(如中科院计算所的DianNao系列论文等),同时带动了电子设计自动化(EDA)技术研究的相应发展。本文对2016年EDA领域的三大国际会议(DATE,DAC和ICCAD)以及DATE 2017上的相关论文进行了总结,展示了当前EDA领域神经网络研究的新热点和新趋势。

EDA领域的神经网络关注的技术

神经网络是计算密集型和存储密集型的应用。在设计神经网络芯片和专用加速器时,需要综合考虑性能、功耗、面积等多种因素。在2016年EDA领域三大会议上收录的论文大都从这些关键问题出发,分别从计算性能优化、访存优化、降低功耗/面积以及编程框架等方面展开研究。

计算性能优化

在使用硬件加速器处理卷积神经网络(CNN)的卷积层操作时,通常存在两种粒度的数据级并行:inter-kernel和intra-kernel。前者挖掘的是CNN层间处理的并行性,在处理特征图片较多的卷积层时性能较好,但数据重用率较低;后者是挖掘同层处理的并行性,数据重用度较高,适用于处理特征图片较少的卷积层,但由于不同网络的卷积层参数变化较大,导致数据映射和数据流设计较为繁琐。为了降低设计难度,论文C-Brain[1]提出了一种通过自身数据级并行调整,来处理多种卷积神经网络的深度学习加速器的方法,可以根据卷积层的不同参数来选择合适的方案实现卷积层操作的并行处理。

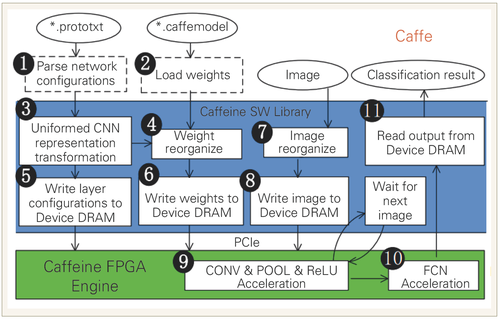

此外,神经网络不同层的计算模式会有一定差别,例如Caffeine[2]通过分析得出神经网络的卷积层是计算密集型,而全连接层则属于访存密集型。在现场可编程门阵列(FPGA)上对CNN/DNN进行加速时,不能只考虑卷积层的加速,否则全连接层的操作会成为系统新的瓶颈。在此基础上,Caffeine分析研究了适用于卷积层和全连接层的神经网络的统一表示方法,以此来减少中间数据的规模;它还设计了一个软硬件协同计算引擎,并对加速器的带宽进行了优化。

访存优化

如何降低神经网络计算中的存储带宽也是目前的研究热点之一。例如在手机等嵌入式设备上部署神经网络加速器时,由于功耗和面积等因素的制约,片上存储容量十分有限。为避免频繁片外访存,需要对网络权值进行压缩,而传统的基于稀疏矩阵的压缩方法造成的随机访存以及在线的编码、解码过程会使访存的吞吐量受限。从访存优化的角度,论文[3]提出了将奇异值分解和剪枝两种技术相结合的方法,在保存模型结构的同时实现了压缩,能够进一步减少模型参数。论文[4]使用“k-means & base-delta”方法对权值数据进行离线编码,大幅度降低了权值数据的存储容量,使在手机等小型嵌入式设备上部署大规模CNN成为可能。论文[5]提出了一种近似乘法器,利用计算单元共享,探索神经网络应用的容错范围和精度损失等参数,来进一步实现访存优化。

降低功耗/面积

功耗和面积是衡量神经网络加速器的重要指标。硬件加速器与图形处理器(GPU)相比,其核心优势主要体现在低功耗和高效能上。从功耗优化的角度来看,论文[6]针对基于阻变式存储器(RRAM)的CNN提出了一种高能效的硬件结构,该结构通过减少模数转换单元,将中间数据用1位来表示,从而将模拟量转换成开关量,以此来降低硬件资源的面积和功耗。论文[7]将MIT(Metal-Insulator-Transition)作为压缩振荡神经元(Compact Oscillation Neuron)的基础器件,与复杂的IF神经元(Integrate-and-Fire Neuron)相比,振荡神经元可以大幅减少面积,因此缓解了外围电路的列间距匹配问题,从而达到降低功耗的目的。此外,由于在人工神经网络(ANN)中突触的数量远远多于神经元的数量,而突触的读写操作也是功耗的重要来源,所以论文[8]从数字电路的角度通过降低电压来提高突触存储的能效。由于传统的6T SRAM内存随电压降低表现出的不稳定性,容易导致计算准确度降低,为此该文采用稳定的8T SRAM代替部分6T SRAM,将对计算较重要的数据高位存储在8T SRAM中,在保证计算准确度的基础上进一步降低电压,达到提高能效的目的。

编程框架

加速器结构的异构性给软件编程带来了严峻的挑战,特别是基于FPGA的硬件加速器设计过程复杂,上层应用开发者可能对底层神经网络结构缺乏了解,导致加速器设计难度和编程难度较大。为简化设计过程,DeepBurning[9]提供了一套基于FPGA的神经网络加速器开发框架(如图1所示)。通过分析常见神经网络的拓扑结构,作者总结归纳出了一系列常用组件(如内积单元、累加单元、池化单元等),通过RTL级描述后形成一套组件库。用户只需提供网络拓扑的上层描述和硬件资源约束,框架中的神经网络集成器即可自动分析网络特征,结合硬件约束在组件库中选出合适的组件搭建硬件网络,以及给出对应的控制流、数据流和数据布局方案。从编程框架的角度,Caffeine分析并研究了适用于卷积层和全连接层的神经网络的统一表示方法(如图2所示),设计了一个软硬件协同计算引擎,并将它与Caffe结合起来,相比于传统的CPU和GPU,有着可观的性能和能效的提升。

图1 神经网络加速器开发框架——DeepBurning

图2 Caffe-Caffeine

神经网络中的新方法

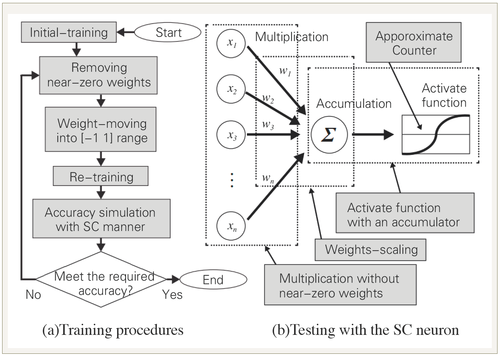

随着神经网络算法的不断迭代,在硬件实现和优化调度方面也出现了一些值得关注的新方法。例如,在DNN中直接采用随机计算能够提升性能,但是存在随机误差波动、范围受限以及累积延迟等诸多问题。为了应对这些挑战,论文[10]提出了一种高效的基于随机计算的DNN实现(如图3所示),采用对权值进行剪枝、权值缩放和累加器集成激励等方法解决上述问题。而针对如何将大规模矩阵映射到小规模网络拓扑结构的问题,论文[11]提出了一种基于随机映射的硬件实现,同时给出了一种面向稀疏矩阵的随机构建方法,以提升FPGA上硬件资源的利用率。从编码的角度,论文[12]提出了一种具有鲁棒性和高效能的脉冲时序神经编码器,该编码器采用脉冲时间间隔编码方案,神经元采用LIF(Leak Integrate and Fire)模型。通过构建神经网络,输入层将模拟信号分解成不同相位差的子信号并分配不同的权重,通过神经网络中间层对信号的处理,实现对脉冲神经网络的高效编码。论文[13]实现了一个 FPGA 加速器 ICAN,其优势在于采用 三维循环展开代替传统的二维展开,使得计算过程更符合卷积运算的特征。为了简化控制逻辑和减少访存次数,论文通过复用输入数据的方法,以牺牲少量的存储来提升数据的局部性,并探讨了如何选取参数达到最佳性能。

图3 (a)DNN训练过程 (b)测试阶段

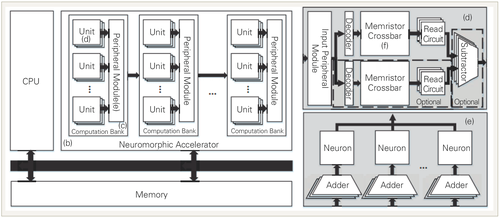

基于忆阻器的加速器研究

基于忆阻器的神经网络计算系统能够明显提高系统的能效,但目前的研究尚缺乏支持早期设计阶段的设计空间搜索仿真平台和模拟系统。针对这一问题,论文[14]提出了一种基于忆阻器的神经网络计算系统的仿真平台——MNSIM(如图4所示),该仿真平台采取分层架构(Computation Bank和Computation Unit),用户可以通过MNSIM提供的接口,配合平台提供的外围设备来进行定制设计。MNSIM嵌入了系统仿真的面积、功耗和延迟等评估模型,能够在原型系统构建早期给出对应的性能评价指标。针对神经网络计算中出现的大量点积操作,论文[15]设计了一套基于忆阻器的神经网络计算系统。该系统由访存控制部件和计算存储部件构成,其中计算存储部件构建于访存控制部件之上,由若干层忆阻器交叉阵列堆叠而成,可在单个计算步长中完成高维度的点积运算。类似的,论文[16]基于多层忆阻器交叉阵列,实现了能够在线训练的仿神经脉冲计算系统,并设计了一套在线自训练算法,能够将权值更新步长缩减50%。

图4 MNSIM的整体结构

神经网络的应用

神经网络作为人工智能领域的重要核心算法,已经被广泛应用到多个场景。例如在容错方面,一个多变的车载环境在计算和通讯中可能产生多种错误,采用人工神经网络可以用来探测并修正错误,但基于软件的实现方式通常不能同时满足硬件截止时间和实时性约束。针对这个问题,论文[17]提出了一种基于FPGA和人工神经网络的容错系统(如图5所示),在有限的硬件资源上,通过复用乘法和加法浮点操作的神经元结构,来提升系统的实时性。

虽然深度神经网络的应用已经十分广泛,但目前仍然很难在一些资源受限的设备上进行本地部署。论文[18]针对移动设备和可穿戴设备能量受限的特点,从加速器结构和算法循环优化的角度出发,实现了一个高效灵活的硬件加速器。该加速器使用了单指令多数据流(SIMD)的计算模式以及向量指令集,并充分利用计算局部性来提升数据的复用,减少访存次数,使之能够嵌入到移动设备中。而在DATE 2017上获得最佳论文的MoDNN[19],则提出了一个在本地部署DNN应用的分布式移动计算系统。该系统可以将训练好的DNN模型分割部署到多个移动设备上,以降低嵌入式设备的计算成本和内存使用。

图5 Zynq上的混合容错电子控制单元模型

结论与发展趋势

我们统计了2016年EDA领域三大会议和DATE 2017上的论文总数以及神经网络相关论文数目(见图6)。从图中可以看到,在2016年,三大会议中神经网络相关论文数分别只有5篇、6篇和 7篇,而2017年仅在DATE会议中,神经网络相关论文数就增加到22篇,这反映了神经网络在EDA领域仍然是目前研究的一个热点。

图6 EDA会议神经网络相关论文数与总发表论文数

针对神经网络的优化,研究主要集中在提高数据的局部性、挖掘计算的并行性、减少权值数据的存储空间以及降低芯片的功耗面积等方面。从采用的技术来看,主要有剪枝、权值压缩、数据共享、数据并行、近似计算等。目前已经有很多研究人员将其他领域的方法迁移到神经网络优化中,以及将新材料应用于神经网络设计中。随着相关研究的不断深入,相信我们会很快看到更多的新思路、新方法,以及新的芯片和软硬件系统(如ISSCC 2017等会议的更多论文)。另外,不可忽视的是,神经网络具有广阔的应用前景,例如在DATE 2016上,相关工作已经将神经网络应用于汽车系统的错误检测[17]及嵌入式移动设备[18],而在DATE 2017上,将深度神经网络应用在移动端设备的工作则获得了最佳论文奖[19],相信神经网络将会在其他领域逐渐涌现出更多更成功的应用。

总的来看,近年来计算机体系结构与EDA两个领域的研究已经接近融合,同时以新型应用为驱动的研究也成为目前的热点。除了软件和算法层面,神经网络还在拓扑结构和编程框架等领域获得了较大程度的发展,同时在硬件体系结构领域也得到了长足的进步,这对我们推动人工智能芯片和智能计算机系统的产业化提供了非常有力的基础。 ■

参考文献:

[1] Song L, Wang Y, Han Y, et al. C-brain: a deep learning accelerator that tames the diversity of CNNs through adaptive data-level parallelization[C]//Proceedings of the 53rd Annual Design Automation Conference(DAC’16). New York: ACM Press, 2016:123.

[2] Zhang C, Fang Z, Zhou P, et al. Caffeine: Towards uniformed representation and acceleration for deep convolutional neural networks[C]//Proceedings of the 35th International Conference on Computer-Aided Design(ICCAD’16). New York: ACM Press, 2016.

[3] Chung J, Shin T. Simplifying deep neural networks for neuromorphic architecttures[C]//Pro- ceedings of the 53rd Annual Design Automation Conference(DAC’16). New York: ACM Press, 2016:126.

[4] Wang Y, Li H, Li X. Re-architecting the on-chip memory sub-system of machine-learning accelerator for embedded devices[C]//Proceedings of the 35th International Conference on Computer-Aided Design(ICCAD’16). New York: ACM Press, 2016:13.

[5] Sarwar S S, Venkataramani S, Raghunathan A, et al. Multiplier-less artificial neurons exploiting error resiliency for energy-efficient neural computing[C]//Proceedings of the 2016 Conference on Design, Automation & Test in Europe(DATE’16). EDA Consortium, 2016:145-150.

[6] Xia L, Tang T, Huangfu W, et al. Switched by input: power efficient structure for RRAM-based convolutional neural network[C]// Proceedings of the 53rd Annual Design Automation Conference(DAC’16). New York: ACM Press, 2016:125.

[7] Chen P Y, Seo J S, Cao Y, et al. Compact oscillation neuron exploiting metal-insulator-transition for neuromorphic computing[C]//Proceedings of the 35th International Conference on Computer-Aided Design(ICCAD’16). New York: ACM Press, 2016:15.

[8] Srinivasan G, Wijesinghe P, Sarwar S S, et al. Significance driven hybrid 8T-6T SRAM for energy-efficient synaptic storage in artificial neural networks[C]//Proceedings of the 2016 Conference on Design, Automation & Test in Europe Conference & Exhibition. IEEE, 2016:151-156.

[9] Wang Y, Xu J, Han Y, et al. DeepBurning: Automatic generation of FPGA-based learning accelerators for the Neural Network family[C]//Proceedings of the 53rd Annual Design Automation Conference(DAC’16). New York: ACM Press, 2016:110.

[10] Kim K, Kim J, Yu J, et al. Dynamic energy-accuracy trade-off using stochastic computing in deep neural networks[C]// Proceedings of the 53rd Annual Design Automation Conference(DAC’16). New York: ACM Press, 2016:124.

[11] Wang Y, Caramanis C, Orshansky M. Exploiting randomness in sketching for efficient hardware implementation of machine learning applications[C]//Proceedings of the 35th International Conference on Computer-Aided Design(ICCAD’16). New York: ACM Press, 2016:114.

[12] Zhao C, Li J, Yi Y. Making neural encoding robust and energy efficient: an advanced analog temporal encoder for brain-inspired computing systems[C]// Proceedings of the 35th International Conference on Computer-Aided Design(ICCAD’16). New York: ACM Press, 2016:115.

[13] Rahman A, Lee J, Choi K. Efficient FPGA acceleration of Convolutional Neural Networks using logical-3D compute array[C]// Proceedings of the 2016 Conference on Design, Automation & Test in Europe(DATE’16). EDA Consortium, 2016:1393-1398.

[14] Xia L, Li B, Tang T, et al. MNSIM: Simulation platform for memristor-based neuromorphic computing system[C]// Proceedings of the 2016 Conference on Design, Automation & Test in Europe(DATE’16), 2016:469-474.

[15] Lastras-Montaño M A, et al. 3D-DPE: A 3D high-bandwidth dot-product engine for high-performance neuromorphic computing[C].Design, Automation & Test in Europe Conference & Exhibition (DATE),2017.

[16] HassanA M, et al. Hybrid spiking-based multi-layered self-learning neuromorphic system based on memristor crossbar arrays[C]. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017.

[17] Shreejith S, Anshuman B, Fahmy S A. Accelerated artificial neural networks on FPGA for fault detection in automotive systems[C]//Proceedings of the 2016 Conference on Design, Automation & Test in Europe(DATE’16). EDA Consortium, 2016:37-42.

[18] Peemen M, Shi R, Lal S, et al. The neuro vector engine: flexibility to improve convolutional net efficiency for wearable vision[C]//Proceedings of the 2016 Conference on Design, Automation & Test in Europe(DATE’16). EDA Consortium, 2016:1604-1609.

[19] MaoJ, et al. MoDNN: Local Distributed Mobile Computing System for Deep Neural Network[C]. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017.

致谢:

本文得到国家自然科学基金(项目编号:61379040),CCF-启明星辰鸿雁基金 (项目编号:CCF-VenustechRP1026002),以及中国科学院青年创新促进会(项目编号: 2017497)的支持。

其他作者:周学海

所有评论仅代表网友意见