我很荣幸应2017中国计算机大会的邀请在会上作特邀报告。这篇短文是基于我在会上的报告整理所得。其他演讲人的报告提到了很多重要的应用,包括计算机视觉、虚拟现实、大数据处理。其中很关键的一个问题就是我们怎么处理这些数据,系统的计算能力能不能跟得上。因而,我把报告题目定为:接近摩尔定律尽端的计算(Computing Near the End of Moore’s Law)。

摩尔定律引发的思考

大家都知道摩尔定律。它说的是平均每18个月(12~24个月都有可能)芯片的晶体管数目会翻倍。图1所示的曲线显示了集成度的增长。可以看到,图中的深蓝色曲线(从上往下第二条)到2000年左右就基本平缓了,由于该曲线表示计算频率的效果,这意味着我们遇到了一个瓶颈。摩尔定律并没有停止,但是登纳德缩放定律(Dennard Scaling)已经停下来了。也就是说,今天无论花费价格的高低,我们能购买到的CPU主频都是2~4 GHz,没有更快的了。其实我们可以做更快的晶体管,例如,前几年美国加州大学洛杉矶分校(UCLA)Frank Chang教授的实验室里就有Tera-Hertz的晶体管出现,但是由于能耗的限制,我们不能把许许多多的Tera-Hertz的晶体管都集成到一个芯片里。所以,2000年初时工业界有一个右转弯,即不增加频率而是增加计算核的个数。到2000年末,我们在思考下一个10年或者20年计算机体系结构领域最大的突破将是什么时,我们的结论是定制化。也就是说,一定要把体系结构与应用相对应,为应用而定制化。其实每个人、每个企业对通用计算的需求往往有限,但对一些特定的计算有较高的需求,要想把这些特定的计算做得很好,更有效的是针对一个领域专门做可定制的计算。据此,2008年我们向美国国家科学基金会提出项目申请,很幸运的是,在2009年我们得到了美国国家科学基金会最大的计算科学研究项目之一——“计算探索”计划1的资助。

图1 摩尔定律与登纳德缩放定律[1]

登纳德缩放定律(Dennard Scaling)

IBM沃森研究中心的登纳德博士在1974提出传统晶体管尺寸与功耗的缩放关系,预测晶体管功耗会随着尺寸变小而同比变小,使相同硅片面积下总功耗保持不变。该定律同时也指出,晶体管尺寸缩小所带来的静态功耗下降,能够抵消频率提高所带来的动态功耗增长,所以设计者在缩小晶体管尺寸的同时,可以通过提高芯片的时钟频率来提升性能。所以在2005年以前,芯片速度得到迅速增长,频率从英特尔4004处理器的740KHz发展到当前主流处理器的3GHz左右。当摩尔定律使晶体管尺寸下降到纳米级时,量子隧穿等现象导致晶体管漏电,使晶体管的静态功耗不减反增,登纳德缩放定律失效,功率密度上升,散热问题加剧。芯片厂商们逐渐停止研发高频芯片,转而研究低频多核的处理器架构。

定制化的计算

为什么要做定制化的计算?我们在写“计算探索”提案时参考了UCLA Ingrid Verbouwhede教授的团队在2003年对一个加密算法的功耗研究。该工作指出,与专用电路的比特率和能耗相比,汇编代码在当时最好的低功耗计算机上的效率要差80多倍,而最好的个人电脑的功耗要差800多倍[2],所以定制和通用计算的效率有巨大的差别。十年后,斯坦福大学Mark Horowitz教授的团队也做了类似的研究,他使用不同的体系结构和多核技术实现了图像处理算法H.264,并且做了一些指令级的优化,但是这样最优化的多核处理器实现与专用电路的性能和效率相比还是相差50多倍[3]。所以,我们想尝试一下能不能用可定制化计算来弥补这个巨大的差距。

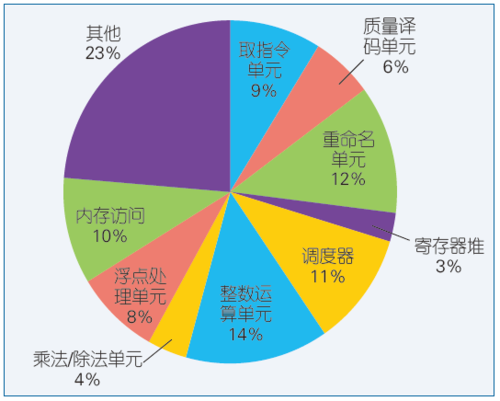

大家可能很好奇:计算机体系结构已经发展六七十年了,为什么会有这么大的差距?我们来看看现在最先进的计算机处理器的能耗花费。计算的每一步需要执行一条指令,我们实验室在2014年的模拟数据(见图2)表明[4],取一条指令需要花费9%的能耗,指令的分析又花费6%的能耗,然后,还需花费12%的能耗对指令中数据的名称进行转换,以减少依赖性的冲突,之后需要重新排序,在数据未到之前先完成其他指令,这一步又消耗11%的能耗,随后还有若干步骤,最后一步才是在加法器和乘法器上做有效计算,计算完成后再把结果写到存储器里。在上述的这些步骤中,其实只有最后一步在做计算,前面的读取指令、分析指令及调度指令,都是在为计算做准备。所以,如果把这些不需要计算的辅助成分去掉,可腾出3倍的芯片面积直接用于计算。

图2 通用处理器流水线的能耗剖析

定制化还有哪些优势?首先,位宽可以优化,因为现在的处理器都是32位或64位,如果只是做图像处理,也许8位就够了;其次,现在的内存系统都有好几层的缓存,数据不停地移来移去,但对于定制的芯片,可以明确地知道何时需要某个数据,从而可以简化。当这些优化都能实现时,就可以有10到100倍的提高。

最近谷歌研制出了一套芯片,专门做人工智能推理的加速处理,计算效率有上百倍的提高[5]。它推出的第二款芯片还可以做机器学习训练的加速。但是我认为每个人或每个企业自己做定制的芯片不是一件容易的事情,设计周期大概是12~24个月,需要投入大量的资金、精力和经验。

我们的想法是不一定每项处理都做定制的芯片,而是在芯片或数据中心里部署众多的可编程和可组合的加速器,来实现各式各样的加速。我们希望以后绝大部分计算都不是在通用计算机上进行,而是在这类加速器上完成,这其实是计算机体系结构的一个很大的变化。现在大多数处理器应用的是经典的冯·诺伊曼体系结构,其中心可以说是一个由指令控制的通用数据流,但我们想做的是各种形式的可定制化计算。

大家可能想问:为什么现在要做这么巨大的转变?1946年世界上第一台通用计算机ENIAC装有18800只电子管。1970年代第一个微处理器里有2200个晶体管。今天的苹果手机里有几十亿个晶体管。早期计算单元很匮乏,而且完全受设备限制,所以需要一个通用的控制结构和数据流来执行所有的指令。但今天的手机里有几十亿个晶体管,它的约束条件就变成没有足够多的能量来满足计算的需求,所以我们要尝试转变。在这里我讲一个小故事。某天早上我跑步时看见路上有一个工人在挖坑,没过两分钟,另一个工人就过来把坑给填了;第一个工人继续往前走,又挖一个,后面那个工人又过来把坑给填了。这个过程重复了若干次。我很不解,就过去问他们为什么这样做。他们的回答是应该有第三个人往坑里放一棵树,但是他那天生病了没有来。这当然是个笑话, 但它说明了一个道理。如果只有几个人时不应该定制化,而是每个人都可以干所有的事情才效率最高;但是如果有几万人或几亿人,定制化就会更有效。所以今天的社会有很仔细的分工。生病一定要看医生而不是律师,有计算机的问题一定找计算机系的老师,而不是中文系的老师。这就是分工的体现。尤其是在这个知识爆炸的时代,对专业化的要求越来越高。

人脑也是定制化计算的一个很好的例子。我们的大脑的功率只有20瓦,但它可以做很复杂的语言处理、图像处理和逻辑思维推理。我问过很多神经学家,他们说没有在大脑里发现一个通用的计算器在一步步的执行指令,大脑里是各式各样的特定的神经网络,有的做语言处理,有的做逻辑思维,有的做运动协调,它们就相当于我所说的加速器。正因为用到了这些各式各样的加速器,我们的大脑的效率才非常高。

工业界最近也在朝这个方向发展。比如,微软数据中心从2014年就开始大规模使用现场可编程门阵列(Field-Programmable Gate Array, FPGA)对搜索工作做加速,百度在此前也启动了FPGA加速工程,尤其是做了深度学习的加速。全球最大的处理器厂家英特尔在2015年以170亿美元收购了全球第二大的FPGA公司Altera,目的是把FPGA广泛应用于数据中心和云计算。目前,亚马逊(Amazon)和阿里巴巴也都在他们云计算的数据中心引入了FPGA。

定制化的层次

定制化有三个层次:芯片层次、服务器层次、数据中心层次。

芯片层次

芯片级定制的多加速器体系结构如图3所示。其中C代表核,多个加速器元件(Accelerator Building Block, ABB)可以通过部分纵横交叉互联结构很快地组合起来。另外,还可以将更小粒度的可编程逻辑组合成ABB。同时,可以把加速器加到存储器里面,使它的存储也实现定制化。同时,我们可以在芯片内部添置一些射频通讯的互联来支持不同节点之间可定制的专用联结。这个联结不是通过在空气中的射频互联,而是通过在芯片上专门设定的波导传输线互联。

图3 芯片级定制:多加速器体系结构[6]

服务器层次

尽管我们做了许多在芯片层次的定制化的研究,但我们并没有制作芯片。为什么?因为研制一个芯片大概需要几千万美元,而且周期很长。所以我们选用了FPGA做定制计算。我们在服务器节点层次上用FPGA来实现各种芯片。FPGA可以实现各种各样的逻辑电路,一旦出现错误还可以重写。它不仅有可编程的计算元件,可用于实现任何有限变量(通常不超过6或7)的二进制函数,还有很多内存和常用的计算单元,而且有可编程的互联。这样的芯片可以在非常短的时间内进行改编,成为一个全新的定制芯片。我们尝试了多种FPGA和服务器的组合。比如,我们把AlphaData公司提供的FPGA加速卡安装在服务器的PCI-e总线上,就可以对各种工作进行加速。为了进一步增大CPU和FPGA之间的带宽,Convey公司把4个FPGA放在服务器的内存总线上;英特尔公司则通过QPI总线来结合FPGA与CPU,最近又将CPU和FPGA放在同一个硅基片上来进一步提高集成度。我们对这些产品也都有所尝试,取得了不少计算加速的好结果。

其中一个很成功的应用是在精准医疗中对DNA序列测定的加速。DNA序列测定可以提供一个准确的诊断和治疗方法,但是测量的过程非常复杂,因为测序仪只能测出100~300个序列,需要通过计算拼出一个30亿长的序列,计算复杂度非常高。我们设计了FPGA芯片来做这个工作。其中有一个多层次的加速器结构,比单个CPU核快了300多倍,比最新的24核服务器快20多倍[7]。之前,DNA测序和分析往往需要几十甚至上百个小时,现在我们大大缩短了时间,只需要4~5个小时就可以完成。此外,在大数据的压缩方面,我们采用英特尔公司提供的CPU与FPGA同在一个硅基片上的芯片,就能实现不丢失任何信息的无损数据压缩,将压缩效率提高30多倍,从300Mb/s提高到10000Mb/s。

数据中心层次

对于很多IT工作者来说,要搭建上述定制化的服务器系统还是比较困难,因为需要自己选购FPGA加速卡等等。所以,当我们把这些定制化系统部署到数据中心里,众多的应用程序开发者就可以远程地使用了。2013年我们用ARM处理器和FPGA开发板搭建出的小集群,使很多学生上课时就可以远程使用并设置自己的加速器,而不必各自搭建硬件平台。进一步,我们在普通服务器的每个节点加入了FPGA加速卡,搭建了几十个节点的机群,并配置了有效的编程环境来支持大数据应用的计算[8]。(编程软件是很重要的,因为待开发的应用需要在复杂的硬件系统上运行。下面一节会专门提到这个问题。)最近,微软把成千上万的FPGA直接连接在数据中心的交换机上,建立了以加速器为中心的的新计算系统结构[9]。

定制计算的编译平台

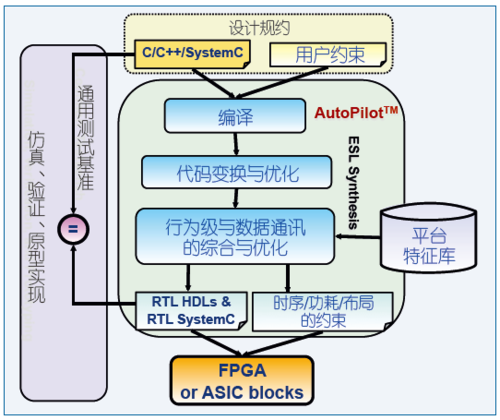

考虑到芯片的设计难度太高,2006年我们做了一项工作,设计了一个编译器把通常用于软件编程的C语言程序自动生成VHDL2或Verilog3硬件设计语言,这项工作称为高层次综合(high-level synthesis)。这个概念在1980年代就有人提出来了,但是转化的效果没有手动设计的好。我们做了各种各样的硬件调度和资源分配上的优化,并且用到了当时最新的编译器架构LLVM4,对C语言进行分析处理并做多层次的优化来有助于生成集成电路。这项工作非常成功和有影响力[10]。我们在2006年成立了技术转化公司AutoESL,到2011年被全球最大的FPGA公司Xilinx并购,其Vivado HLS高层次综合工具就是源于我们的工作,目前已被近2000篇学术论文引用。

图4 基于C/C++语言的加速器设计综合[10]

AutoESL被收购后,我们进一步开发定制计算的编译平台。我们发现C语言的代码风格对高层次综合的结果有很大的影响。而许多软件开发者缺少硬件设计背景,很难写出适合高层次综合的C语言程序。所以我们做了很多的源码到源码等价转换的研究,希望可以自动地将原来的C语言直接变成面向硬件化的C语言。同时,我们做了很多的优化,让很多高级程序设计语言(如Spark或Caffe)都可以自动生成面向芯片的语言。

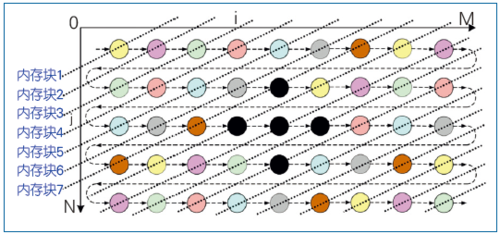

图像处理中经常遇到图5所示的stencil计算:黑色的五个点中,位于中间的那个点的某些信息需要利用它周围四个点的信息一起计算得到。其实在硬件上要想很快地处理出来,要求这五个点的信息同时从内存里读出来是不容易的,因为FPGA上的内存只有两个数据端口。一个方法是把原来的图像拷贝5份,但是这样不够高效。更巧妙的方法是把一个数据组划分为若干小数据组存储在不同的内存块,例如,按奇偶数分开,需要用6~7个内存块,但这显然不是最优的结果。2014年我们发现更优的结果是完全为stencil计算定制的,不再用普通的存储体,而是用FIFO把它结合起来。首先把数据放进去,然后每做一个新的点时可以往前移,需要的数据可以从4个存储体中读取出来。从理论上可以证明数据的移动和存储体的个数是最小的[11]。最近,我们又研究了如何同时处理多个点的问题,提出将数据链重新组合的理论,将数据读取和重用定制化,并且自动生成描述这种微处理结构的C语言。

图5 图像处理应用示例

我们的另一个工作是从C语言开始做各式各样的分析和优化,然后完全自动化地生成OpenCL语言来支持基于FPGA和GPU的异构计算。如果不做这些优化,直接写OpenCL程序的话,效率可能会相差20多倍。这项工作主要由我们的技术转化公司Falcon Computing进一步开发,实现了Merlin编译器专用于支持定制计算,在此基础上我们做了不少新的工作,比如用FPGA对机器学习进行加速。但是实现好的机器学习加速器工作量还是很大的,大概需要编写十万行硬件描述语言代码,即使高层次综合C语言也需要几百行代码。而现在大多数学者用描述性的模型实现机器学习,大概只有十几行代码。差距还是很大,所以我们基于Merlin编译器把从机器学习的描述性的模型到定制化硬件这个过程实现了自动化[12]。

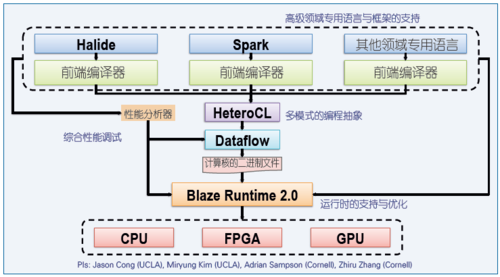

我们最新的工作是一个由英特尔公司和美国国家科学基金会联合资助的项目。我们计划利用多模式的中间语言来支持各种异构系统的编程(见图6)。在这个基础上我们可以支持各种领域专用语言以及技术,例如图像处理领域的Halide语言、大数据处理领域的Spark框架、深度学习领域的Caffe和TensorFlow等等。通过中间语言,我们还可以用到Falcon Computing公司的Merlin编译器和Kestrel运行时系统,并将其应用到CPU、GPU和FPGA层次上。我们还会开发面向这种异构系统的程序性能分析和调试工具。

图6 多模式的异构体系结构编程平台

展望

当我们走近摩尔定律的尽头,计算机的体系结构会有很大的变化。这对研究计算机体系结构的学者来说是一个很好的时机。我深信未来的计算会以加速器为主,而且加速器要可编程、可定制。所以我们研究组的目标很简单,就是让芯片设计和可定制计算“民主化”,让它不再只是少数有多年集成电路设计经验的专家可以做的事,而是让众多的软件工程师也可以有效地用到可定制计算。我们的口号是“You Inovate, We Automate”。你们负责构想各式各样有意思的算法和应用,我们负责把所有与计算平台分配与设计相关的工作自动化,帮助你们实现可定制计算。 ■

致谢:

请让我感谢跟我合作的UCLA、美国莱斯大学(Rice)、加州大学圣芭芭拉分校(UCSB),俄亥俄州立大学(Ohio State),和康奈尔大学(Cornell)的多位教授,北京大学高能效计算与应用中心的老师们,以及参与我们研究工作的所有学生们。

(本文根据CNCC 2017特邀报告整理而成)

整理者:罗国杰 CCF专业会员。北京大学新体制研究员,北京大学高能效计算与应用中心执行主任。主要研究方向为电子设计自动化、基于FPGA及新型器件的异构计算、医学图像分析算法。gluo@pku.edu.cn

脚注:

1 笔者于2010年3月发表在《中国计算机学会通讯》上的《UCLA领域专用计算中心简介》一文中介绍了这个研究项目。

2 全名为Very-high-speed Integrated Circuit Hardware Description Language,是一种用于电路设计的标准硬件描述语言,诞生于1982年。

3 全称为Verilog HDL,是一种硬件描述语言,以文本形式来描述数字系统硬件结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。VHDL和Verilog HDL是世界上最流行的两种硬件描述语言,

4 LLVM是构架编译器(compiler)的框架系统,用C++编写而成,用于优化以任意程序语言编写的程序的编译时间(compile-time)、链接时间(link-time)、运行时间(run-time)以及空闲时间(idle-time),对开发者保持开放,并兼容已有脚本。

参考文献:

[1] Sutter H. The Free Lunch is Over: A Fundamental Turn Toward Concurrency in Software[J]. Dr. Dobb’s Journal, 2005, 30(3).

[2] Schaumont P, Verbauwhede I. Domain-specific codesign for embedded security[J]. IEEE Computer, 2003, 36(4): 68-74.

[3] Hameed R, Qadeer W, Wachs M, et al. Understanding sources of inefficiency in general-purpose chips[C]// Proceedings of the 37th annual international symposium on Computer architecture (ISCA’10), 2010.

[4] Cong J, Ghodrat MA, Grigorian B, et al. Accelerator-Rich Architectures: Opportunities and Progresses[C]// Proceedings of the 51st Annual Design Automation Conference (DAC’14), 2014: 1-6.

[5] Jouppi NP, Young C, Patil N, et al. In-Datacenter Performance Analysis of a Tensor Processing Unit[C]// Proceedings of the 44th Annual International Symposium on Computer Architecture (ISCA’17), 2017.

[6] Chen YT, Cong J, Michael G, et al. Customizable Computing - Synthesis Lectures on Computer Architecture[M]. Morgan and Claypool Publishers, 2015.

[7] Chen YT, Cong J, Lei J, et al. A Novel High-Throughput Acceleration Engine for Read Alignment[C]//IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM’15), 2015: 199-202.

[8] Cong J, Huang M, Wu D, et al. Invited - Heterogeneous datacenters: options and opportunities[C]//Proceedings of the 53rd Annual Design Automation Conference (DAC’16), 2016: 16.

[9] Caulfield AM, Chung ES, Putnam A, et al. A cloud-scale acceleration architecture[C]//49th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO’16), 2016, (99): 1-13.

[10] Cong J, Liu B, Neuendorffer S, et al. High-Level Synthesis for FPGAs: From Prototyping to Deployment[J]. IEEE Trans. Comput. Des. Integr. Circuits Syst, 2011, 30(4): 473-491.

[11] Cong J, Li P, Xiao B, et al. An Optimal Microarchitecture for Stencil Computation Acceleration Based on Non-Uniform Partitioning of Data Reuse Buffers[C]// Proceedings of the 51st Annual Design Automation Conference (DAC’14), 2014, 35(3): 1-6.

[12] Wei X, Hu H. Automated Systolic Array Architecture Synthesis for High Throughput CNN Inference on FPGAs[C]//Proceedings of the 54th Annual Design Automation Conference (DAC’17), 2017.

![图1 摩尔定律与登纳德缩放定律[1] 图1 摩尔定律与登纳德缩放定律[1]](..\..\upload\resources\image\2017\12\11\48886_500x500.png)

![图3 芯片级定制:多加速器体系结构[6] 图3 芯片级定制:多加速器体系结构[6]](..\..\upload\resources\image\2017\12\11\48888_500x500.png)

所有评论仅代表网友意见